Workshop on Accelerator Architectures for the Masses

|

Call for Papers |

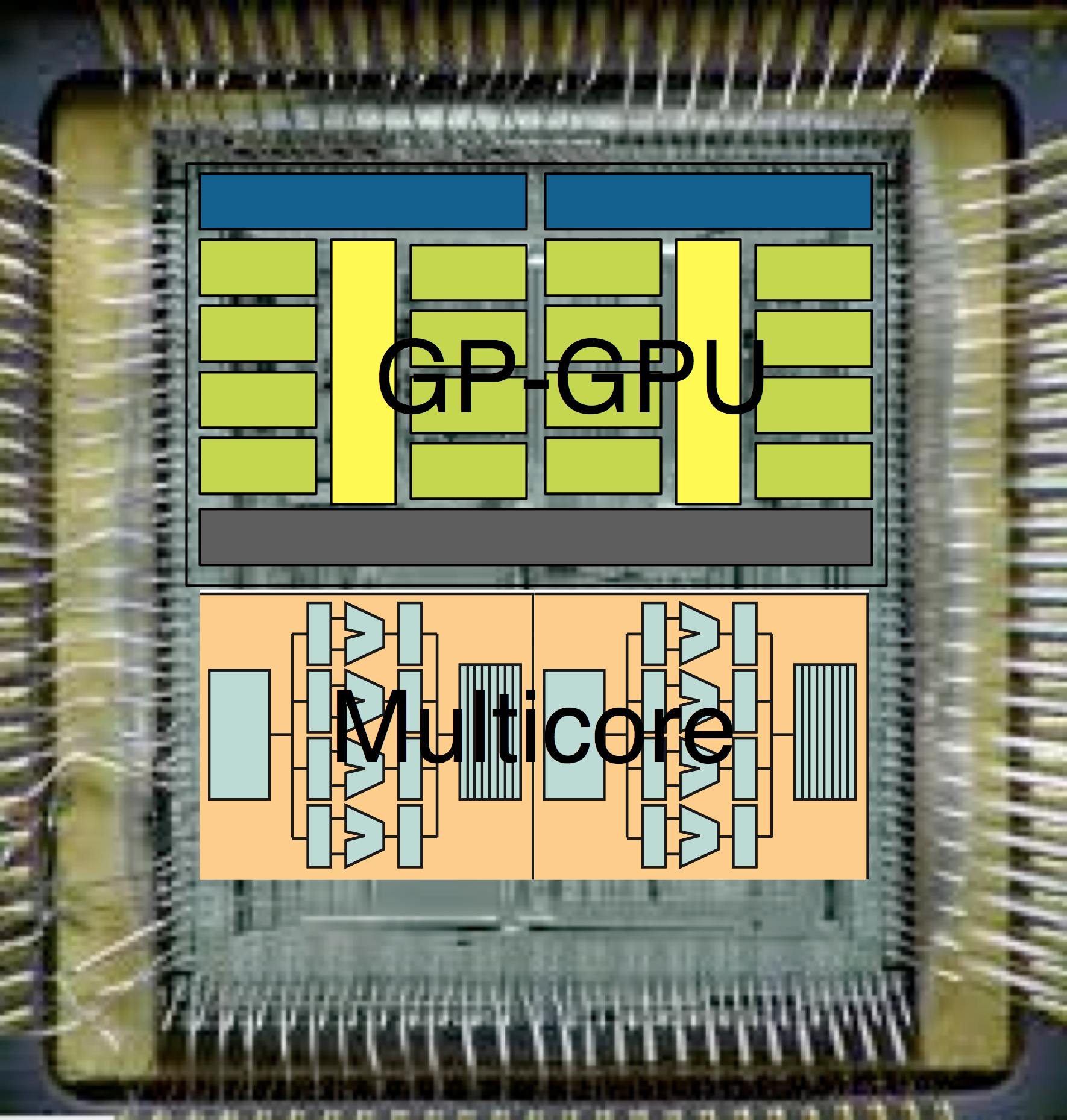

| As we move into an energy-constrained era,

current general-purpose multicore processors will find it increasingly

hard to scale up to application requirements in an efficient

manner. This workshop envisions a radically different future in which

the multicore chip includes specialized accelerator cores that take

care of the bulk of the computation. We are already headed in this

direction; 4 out of the Top 5 fastest supercomputers are hybrid

designs based on GP-GPUs. Mainstream multicore chips already include

diverse accelerators such as GP-GPUs and Cryptographic units. Vendors

promise to deliver plenty more accelerators if we can figure out what

needs acceleration and how to harness these diverse types of cores.

These heterogeneous manycore chips that integrate novel accelerator

units with general-purpose processors promise high levels of

performance and energy-efficiency. At this time, there is a critical

need for research to enable widespread use of manycore accelerators

and GPUs across a wide variety of mainstream applications and

programming paradigms WACy'11 will be co-located with ICS 2011 in Tucson, Arizona. The workshop program will include presentations of peer-reviewed papers as well as a keynote. The organizing committee is soliciting presentations on any topic related to compute accelerators, including

|

Paper submission |

|

Authors are invited to submit original work that advocates new architectures, develops software support, or reports on actual experience. Papers should be submitted in the double column ACM SIG proceedings format, and are limited to 6 pages. Accepted papers will be available to participants at the meeting and will also be posted on our workshop website. The authors of the top two highly ranked papers will be provided an opportunity to formally publish their work in the IEEE Computer Architecture Letters. Submission website : EASY Chair Link |

Important dates |

|

Submissions due: 15th April 2011, 11:59 PST ( Pacific Standard Time ) (Abstracts can be submitted as early as April 8th)

|

Organizing Committee |

Workshop organizers

Arrvindh Shriraman (Simon Fraser University)

Rajeev Balasubromanian,

University of Utah |